SoCs

Showing all 11 results

-

DSBGA-8 footprint for the smallest prototypes and z-height budgets.

-

Full MSPM0C1104 feature set (24-MHz M0+, 12-bit ADC, UART/I²C/SPI) in a minuscule package.

-

Explicit X-device status to de-risk production—prototype now, change package later.

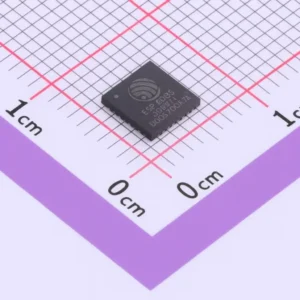

- Tri-radio on one chip: Dual-band Wi-Fi 6 + BLE 5 + IEEE 802.15.4 for Thread/Zigbee in a single, compact MCU.

- Security built-in: Secure boot, XTS-AES memory encryption, HMAC, RSA/ECC/ECDSA, TRNG, APM & PMP hardening—ready for zero-trust IoT.

- Designed for battery life: LP RISC-V core, deep-sleep with LP SRAM retention, Wi-Fi TWT, and fine-grained PMU control.

- Tri-radio in one chip: Wi-Fi 6 + Bluetooth LE 5.3 + 802.15.4 (Zigbee/Thread) with built-in coexistence on a single antenna.

- Secure by design: Secure boot, XTS-AES flash encryption, digital signature, RSA/ECC, and HMAC in hardware.

- Ultra-low power: Deep-sleep around 7 µA with LP-SRAM retention and Target Wake Time to extend battery life.

- Low power without compromises – Deep-sleep around 7 µA with LP memory retention, fast wakeup, and flexible PMU states. ETM and GDMA enable peripheral-driven data paths so your CPU can nap.

- Security you can ship – Secure Boot, flash encryption, and a full hardware crypto suite (AES/SHA/RSA/ECC/ECDSA/HMAC), plus a power-glitch detector and true RNG, help protect firmware/IP and elevate trust.

- Radio versatility – Bluetooth LE 5.3 with 2 M and Coded PHY for either speed or range, plus 802.15.4 for Thread/Zigbee/Matter—covering the majority of modern IoT transports with one tiny chip.

-

Dual-core HP RISC-V up to 360 MHz + LP RISC-V up to 40 MHz for always-on tasks.

-

Rich vision & video engine: JPEG codec, ISP (1080p), PPA (scale/rotate/blend), H.264 encoder (1080p@30 fps).

-

Comprehensive security: Secure Boot, XTS-AES flash/PSRAM encryption, TRNG, RSA/ECDSA/HMAC/SHA accelerators, and access-permission management.

- USB device/host ready: Full-speed USB OTG with on-chip PHY streamlines accessories and field update paths.

- ULP always-on sensing: A dedicated ULP coprocessor handles RTC GPIO/ADC/touch while the main CPU sleeps.

- Hardened security chain: Secure boot + flash encryption + hardware AES/SHA/RSA and true RNG.

-

USB all the things: Native USB 2.0 Full-Speed OTG plus a built-in USB-Serial/JTAG device for programming, logging, and on-chip debug with minimal parts.

-

Vision & UI ready: Parallel LCD (8–16-bit RGB/I8080/6800) and DVP camera interfaces up to 40 MHz, with YUV/RGB conversions for low-cost displays and sensors.

-

Hardened by design: Secure Boot, Flash Encryption, AES-128/256, SHA-2, RSA up to 4096-bit, HMAC, Digital Signature, and TRNG for modern, production-grade security.

-

Quad-core Cortex-A55 up to 2.0 GHz for responsive, power-efficient embedded compute.

-

1 TOPS NPU + Mali-G52 GPU for edge AI and modern graphics/compute APIs.

-

4Kp60 decode, 1080p60 encode, and multi-display support for rich media scenarios.

-

Quad-core Cortex-A55 up to 2.0 GHz for responsive, power-efficient embedded compute.

-

1 TOPS NPU + Mali-G52 GPU for edge AI and modern graphics/compute APIs.

-

4Kp60 decode, 1080p60 encode, and multi-display support for rich media scenarios.

- 8-core 8 nm CPU with 6 TOPS NPU: Flagship compute and AI acceleration for demanding edge workloads.

- 8K-class multimedia engine: Decode 8K60, encode 8K30, and drive multi-display setups up to 8K@60.

- Rich, modern I/O: PCIe 3.0, USB 3.1, SATA 3.0, GbE, and flexible camera/display interfaces.

- 6 TOPS on-chip NPU for private, low-latency AI at the edge.

- 8K60 decode + 8K30 encode for premium playback, recording, and signage.

- Dual 48MP ISP with HDR/3DNR for multi-camera vision systems.