XC2C256-6FTG256C Xilinx XC2C256-6FTG256C CoolRunner-II CPLD FPGA | 256 Macrocells | Ultra-Low Power | 1.8V Optimized

The Xilinx XC2C256-6FTG256C is a low-power, high-performance CPLD with 256 macrocells, 5.7ns pin-to-pin delays, and multi-voltage I/O (1.5V–3.3V). Ideal for battery-powered and high-speed logic designs.

Key Features:

✅ Ultra-Low Power – 13μA quiescent current, DataGATE for dynamic power reduction

✅ High-Speed Logic – 5.7ns pin-to-pin delay, DualEDGE flip-flops for 2x efficiency

✅ Flexible I/O Banking – Supports LVCMOS, LVTTL, SSTL, HSTL (1.5V–3.3V)

Xilinx XC2C256-6FTG256C CoolRunner-II CPLD Ultra-Low Power, High-Speed Programmable Logic Solution

The Xilinx XC2C256-6FTG256C is part of the CoolRunner™-II CPLD family, designed for power-sensitive and high-performance logic applications. With 256 macrocells, 5.7ns propagation delays, and dynamic power-saving features, it provides an optimal balance of speed and efficiency for embedded systems, communication interfaces, and industrial control.

Key Features & Benefits

1. Ultra-Low Power Consumption

- 13μA quiescent current (standby) – Ideal for battery-powered devices

- DataGATE™ technology – Disables unused inputs to reduce dynamic power

- 1.8V core voltage – Optimized for modern low-power designs

2. High-Speed Performance

- 5.7ns pin-to-pin delay – Fast signal processing for real-time control

- DualEDGE flip-flops – Doubles throughput at half the clock speed

- CoolCLOCK™ technology – Divides clock frequency to reduce EMI/power

3. Flexible I/O & Interfacing

- 1.5V–3.3V multi-voltage I/O – Supports LVCMOS, LVTTL, SSTL, HSTL

- 2 I/O banks – Independent voltage translation (e.g., 3.3V ↔ 1.8V)

- Schmitt-trigger inputs (per pin) – Noise immunity for industrial environments

4. Advanced Programmability

- IEEE 1532 (JTAG) in-system programming – Fast 1.8V ISP

- PLA architecture – 100% pin retention & product-term routability

- Open-drain outputs – Supports wired-OR & LED driving

5. Robust System Integration

- Clock management – Divide-by-2/4/6/8/10/12/14/16 options

- Hot-pluggable – Safe for live insertion/removal

- IEEE 1149.1 boundary scan – Simplified PCB testing

Technical Specifications

| Parameter | Specification |

|---|---|

| Device | XC2C256-6FTG256C |

| Macrocells | 256 |

| Propagation Delay | 5.7ns (max) |

| Quiescent Current | 13μA (typical) |

| Core Voltage | 1.8V |

| I/O Voltages | 1.5V, 1.8V, 2.5V, 3.3V |

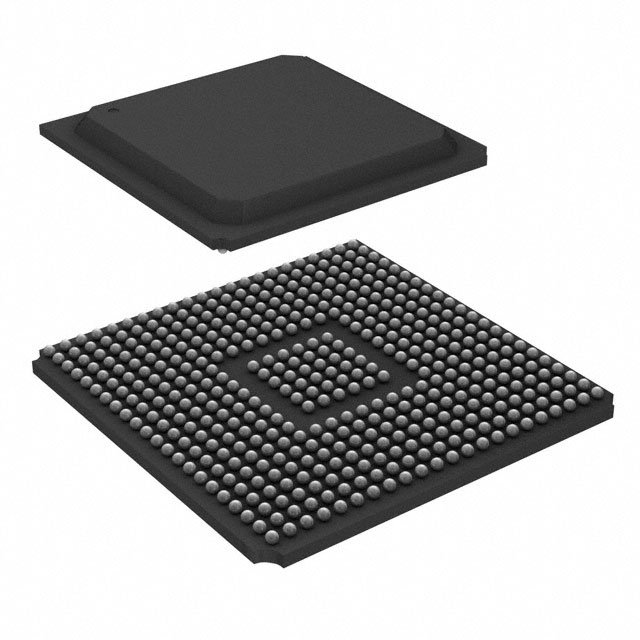

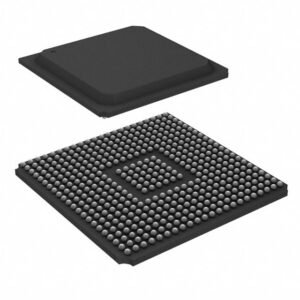

| Package | 256-ball FT (1.0mm) BGA |

| User I/O | 184 |

| Clock Management | DualEDGE, CoolCLOCK, Global Set/Reset |

| I/O Standards | LVCMOS, LVTTL, SSTL2/3, HSTL-1 |

| Security | Advanced bitstream encryption |

Applications

🔋 Portable Electronics – Wearables, handheld devices

📡 Communications – UART, SPI, I²C bridging

🏭 Industrial Control – PLCs, motor controllers

🔌 Interface Translation – Level shifting (1.8V ↔ 3.3V)

Package Options

The XC2C256-6FTG256C comes in a 256-ball Fine-Pitch BGA (FT, 1.0mm) with 184 user I/O. Alternative packages for smaller designs:

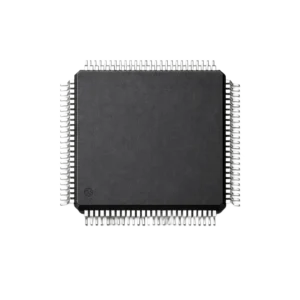

- 144-pin TQFP (118 I/O)

- 208-pin PQFP (173 I/O)

- Pb-free options available

Competitive Advantages

| Feature | XC2C256-6FTG256C | Altera MAX II | Lattice ispMACH 4000 |

|---|---|---|---|

| Power Efficiency | 13μA standby | 50μA | 25μA |

| Speed | 5.7ns delay | 7.5ns | 6.5ns |

| I/O Flexibility | 1.5V–3.3V | 3.3V only | 2.5V–3.3V |

| Clocking | DualEDGE + CoolCLOCK | Basic PLL | None |

Why Choose CoolRunner-II? Best power-speed tradeoff for mixed-voltage systems.

Design Tools & Support

🛠️ Xilinx ISE WebPack – Free synthesis/programming tools

📖 Pre-verified IP cores – UART, SPI, PWM logic

🔄 IEEE 1532 JTAG – Fast field updates

Order the XC2C256-6FTG256C Today!

📞 Contact us for volume pricing & technical support!

Who Uses This CPLD?

- Embedded Engineers – Glue logic, power management

- Consumer Electronics – Smart remotes, IoT edge nodes

- Automotive – Sensor interfacing, CAN bus logic

🔧 Backed by Xilinx’s ecosystem – Datasheets, reference designs, and forums.

Specification: Xilinx XC2C256-6FTG256C CoolRunner-II CPLD FPGA | 256 Macrocells | Ultra-Low Power | 1.8V Optimized

|