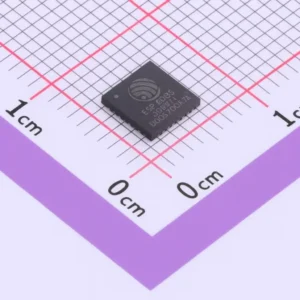

ESP32-P4 ESPRESSIF ESP32-P4 RISC-V MCU — High-Performance Vision, Voice & Connectivity

-

Dual-core HP RISC-V up to 360 MHz + LP RISC-V up to 40 MHz for always-on tasks.

-

Rich vision & video engine: JPEG codec, ISP (1080p), PPA (scale/rotate/blend), H.264 encoder (1080p@30 fps).

-

Comprehensive security: Secure Boot, XTS-AES flash/PSRAM encryption, TRNG, RSA/ECDSA/HMAC/SHA accelerators, and access-permission management.

ESP32-P4 Product Overview, Specifications & Applications for Embedded AI, HMI and IoT

ESPRESSIF’s ESP32-P4 is a next-generation, high-performance 32-bit RISC-V microcontroller designed for connected products that need serious local processing for graphics, imaging, and voice. The device combines a High-Performance (HP) subsystem with a dual-core RISC-V CPU running up to 360 MHz, and a Low-Power (LP) subsystem with a separate 32-bit RISC-V core up to 40 MHz for housekeeping and always-on tasks. Together, they deliver responsive UIs and multimedia features without sacrificing standby efficiency.

At the heart of ESP32 P4 is a modern memory subsystem tailored for bandwidth-hungry workloads: 128 KB HP ROM, 16 KB LP ROM, 768 KB HP L2MEM, 32 KB LP SRAM, and an 8 KB system scratchpad (SPM). The chip also integrates in-package PSRAM—available in 16 MB or 32 MB variants—so graphics buffers and model tensors can live on-package with minimal board-level complexity. The memory controller supports up to 64 MB PSRAM with XTS-AES protection and flexible cache mapping for instruction and data spaces.

For multimedia, ESP32-P4 packs a hardwired JPEG codec (up to 4K stills, 1080p@40 fps encode/decode), an Image Signal Processor (ISP) with a full pipeline up to 1080p, a Pixel-Processing Accelerator (PPA) for scaling/rotation/blending, and a baseline H.264 encoder up to 1080p@30 fps—an unusually rich set for an MCU-class device. These blocks offload the CPU, enabling power-efficient image capture, preview, overlay composition, and video encoding at the edge.

On the I/O side, ESP32-P4 exposes 55 programmable GPIOs and a broad mix of interfaces: MIPI-CSI for cameras, MIPI-DSI for displays, USB 2.0 OTG (high-speed & full-speed PHYs), 10/100 Ethernet MAC, SD/MMC Host (SDIO 3.0), I3C/I²C/SPI/I²S/UART, motor- and LED-class PWMs, RMT for precise waveforms, a parallel I/O engine, and more—giving engineers the flexibility to design anything from camera-equipped HMIs and POS kiosks to voice assistants and smart appliances.

Security is first-class: secure boot, eFuse-backed keys, XTS-AES encryption for external memory, TRNG, and hardware accelerators for AES, RSA/DSA, ECDSA (P-192/P-256), HMAC, and SHA-1/2 up to SHA-512/t. Access-permission management (APM/PMS) allows privilege separation across cores, DMA masters, memories and peripherals, supporting robust partitioning between application domains.

Whether your design is a camera-centric edge node, an HMI with fluid graphics, a USB-centric device, or a low-power voice terminal, ESP32-P4 provides the compute, memory, interfaces, and security foundation to ship compelling products at scale. Espressif’s datasheet also highlights target end products such as smart home, healthcare, industrial automation, retail terminals, edge vision, HMI panels, and multimedia players.

Detailed Specifications

| Parameter | Description |

|---|---|

| CPU architecture | HP subsystem: 32-bit RISC-V dual-core up to 360 MHz; LP subsystem: 32-bit RISC-V single-core up to 40 MHz. |

| CoreMark® | 2489.62 at 360 MHz (dual-core); 6.92 CoreMark/MHz. |

| On-chip memories | 128 KB HP ROM; 16 KB LP ROM; 768 KB HP L2MEM; 32 KB LP SRAM; 8 KB SPM. |

| In-package PSRAM | 16 MB (OPI/HPI) or 32 MB (OPI/HPI) options (ESP32-P4NRW16 / ESP32-P4NRW32), 1.8 V; supports up to 64 MB, 200 MHz. |

| External flash/PSRAM | Up to 64 MB external flash with XTS-AES; flexible 64 KB block mapping into instruction/data space via cache; SPI/Dual/Quad/QPI up to 120 MHz. |

| GPIO | 55 programmable GPIOs, including 5 strapping pins. |

| MIPI-CSI (camera) | 2-lane D-PHY v1.1, 1.5 Gbps per lane; supports RGB888/666/565, YUV422/420, RAW8/10/12. Uses dedicated pins 42–48. |

| MIPI-DSI (display) | 2-lane D-PHY v1.1, 1.5 Gbps per lane; input RGB888/666/565/YUV422; output RGB888/666/565. Dedicated pins 34–40. |

| ISP | Full pipeline to 1920×1080; inputs RAW8/10/12; outputs RAW8/RGB888/RGB565/YUV422/YUV420; AE/AF/AWB/Histogram, etc. |

| JPEG codec | 4K still encode/decode; dynamic 1080p@40 fps / 720p@70 fps. |

| H.264 encoder | Baseline profile, up to 1080p@30 fps; I/P frames; dual-stream (total ≤1080p@30 fps). |

| PPA (graphics) | Hardware scale/rotate/mirror; alpha-blend two layers; multiple RGB/YUV formats. |

| Display/Camera ctrl. | LCD_CAM: parallel 8/16/24-bit LCD (RGB, 8080, 6800) and DVP camera; simultaneous LCD+camera; GDMA moves frames. |

| USB | USB 2.0 OTG, High-Speed + Full-Speed PHYs; integrated USB-Serial-JTAG. |

| Ethernet | 10/100 EMAC; RMII signals routed via GPIO matrix. (See consolidated pin table for GMAC functions.) |

| Storage | SD/MMC Host (SDIO 3.0). |

| Serial interfaces | Five UART + 1 LP UART (up to 5 MBaud, DMA, flow control), four SPI + LP SPI, two I²C + LP I²C, I3C master/slave, three I²S + LP I²S. |

| Timers & WDT | Two 52-bit system timers; timer groups with 54-bit counters; HP/LP watchdogs plus analog super watchdog. |

| PWM / control | LEDC (LED PWM), MCPWM (motor), RMT (remote control), PCNT (pulse count), Parallel I/O (PARLIO), BitScrambler. |

| Analog | Two ADC controllers, touch sensor (14 ch, sleep-capable, wake), temperature sensor, analog comparator. |

| Security | Secure Boot, eFuse OTP, TRNG, AES/ECC/HMAC/RSA/SHA accelerators, DSA/ECDSA, XTS-AES for external memory; Access-Permission Management (PMS/APM). |

| Low-power modes | Active, Light-sleep, Deep-sleep; LP memory/LP peripherals can remain powered in deep sleep; RTC/host events wake. |

| Boot & download | SPI Boot; Joint Download Boot via USB (USB-Serial-JTAG or USB 2.0 OTG), UART, or SPI-slave; configurable strapping pins with latch behavior. |

| DMA | General-purpose GDMA, VDMA, and 2D-DMA with macroblock reordering & color-space conversion to serve JPEG/PPA pipelines. |

| Typical applications | Smart home, industrial automation, healthcare, consumer electronics, smart agriculture, retail POS/vending, service robots, multimedia players, streaming cameras, USB host/device, smart voice terminals, edge vision AI, HMI panels. |

Applications

Human–Machine Interfaces (HMI) & Dashboards. Pair ESP32-P4 with a MIPI-DSI or parallel RGB display to build responsive control panels and infotainment UIs. The PPA accelerates rotation, scaling, and blending, while the LEDC/MCPWM blocks drive status and backlight control. For camera-equipped panels or kiosks, the LCD_CAM controller and ISP enable simultaneous capture and display pipelines with minimal CPU overhead.

Vision at the edge. With a 2-lane MIPI-CSI input (up to 1.5 Gbps/lane), ISP up to 1080p, JPEG encode/decode, and H.264 baseline encoding at 1080p@30 fps, ESP32-P4 can capture, preprocess, compress, and stream frames to the cloud or a host over Ethernet, USB, or SDIO. Use the PPA to crop/scale overlays and watermark frames on-chip before transmission.

Smart voice and audio terminals. The LP system keeps keyword detection and housekeeping alive in deep sleep; the HP system wakes to run voice pipelines. With multiple I²S interfaces (plus LP-I²S for low-power audio), TRNG and crypto accelerators for secure auth, and USB HS device/host, you can implement secure audio endpoints or accessories that stream over USB or Ethernet.

USB-centric devices. Dual USB 2.0 OTG PHYs (HS and FS) with an integrated USB-Serial-JTAG controller simplify manufacturing, firmware download, diagnostics, and rich peripheral/host roles—handy for accessories, POS, and storage front-ends via SD/MMC.

Industrial and home appliances. With 55 GPIOs, motor-control PWM (MCPWM), ADCs, touch keys, comparators, watchdogs, and permission controls, ESP32-P4 can implement robust, safety-minded control loops and HMI, while secure boot and memory encryption protect firmware IP and configuration data.

Retail self-service & kiosks. MIPI-DSI displays, barcode camera input via CSI/DVP, and video compression allow low-cost terminals that can record or stream sessions securely over Ethernet/USB.

Why engineers choose ESP32-P4

-

Compute where it counts: The dual-core HP RISC-V at up to 360 MHz (with path to 400 MHz on request) gives you headroom for GUI frameworks, protocol stacks, and local models, while the LP core handles RTC, wake logic, and low-duty tasks without burning battery.

-

Display- and camera-first design: Native MIPI-CSI/DSI, a full ISP, and H.264/JPEG ensure most vision/graphics workflows stay in hardware, reducing software complexity and power.

-

End-to-end security: From secure boot and eFuse to TRNG and accelerators (AES/HMAC/RSA/ECDSA/SHA) plus XTS-AES for external memories and PMS/APM for isolation, the device is built for products that must resist tampering and protect assets in the field.

Three bite-size highlights

-

Vision pipeline on-chip: ISP + JPEG + H.264 + PPA turns raw sensor data into compressed video with overlays—no external codec needed.

-

Memory to match your UI: In-package 16 MB or 32 MB PSRAM options simplify PCB design and keep framebuffers local; up to 64 MB PSRAM supported.

-

Secure by default: Secure boot, TRNG, XTS-AES for flash/PSRAM, and hardware RSA/ECDSA/HMAC/SHA accelerators.

Design notes & integration tips

-

Boot and provisioning. Strapping pins (GPIO34–38) determine boot modes; latches capture state at reset, freeing the pins for IO later. Joint Download Boot supports USB (USB-Serial-JTAG and USB OTG), UART, and SPI-slave download. This streamlines factory flashing via a single USB port.

-

Low-power strategy. Use Light-sleep for quick resume (CPU paused, most blocks can be power-gated) and Deep-sleep for longest battery life (CPU/L2MEM off; LP memory/peripherals can remain on). The LP watchdog and RTC timers can wake the system.

-

DMA for pixels. Leverage GDMA/VDMA and the specialized 2D-DMA with macroblock reordering and color-space conversion to feed JPEG/PPA efficiently, minimizing CPU copies.

-

USB & Ethernet pinout. High-speed/Full-speed USB PHY pins (DM/DP) and RMII signals are mapped in the consolidated pin list; plan power domains (e.g., VDD_USBPHY, VDD_IO) accordingly.

-

Secure partitioning. Use the APM/PMS to assign address-range permissions per DMA master and per CPU core across internal/external memories and peripheral registers. This helps enforce least privilege between UI, connectivity, and sensor tasks.

Example application ideas

-

1080p streaming camera with MIPI-CSI sensor: ISP → PPA overlay → H.264 encode → stream over USB HS or Ethernet; store snapshots to SDIO.

-

Touch HMI panel using MIPI-DSI or RGB parallel LCD: PPA scales UI assets; LEDC handles backlight; touch sensor provides buttons/sliders, even during sleep.

-

USB multifunction accessory (audio + storage + debug): USB-Serial-JTAG simplifies logging; SD/MMC hosts removable media; cryptography blocks secure file access and firmware.

Specification: ESPRESSIF ESP32-P4 RISC-V MCU — High-Performance Vision, Voice & Connectivity

|