ESP32-H2 ESPRESSIF ESP32-H2 Bluetooth LE & IEEE 802.15.4 MCU

- Low power without compromises – Deep-sleep around 7 µA with LP memory retention, fast wakeup, and flexible PMU states. ETM and GDMA enable peripheral-driven data paths so your CPU can nap.

- Security you can ship – Secure Boot, flash encryption, and a full hardware crypto suite (AES/SHA/RSA/ECC/ECDSA/HMAC), plus a power-glitch detector and true RNG, help protect firmware/IP and elevate trust.

- Radio versatility – Bluetooth LE 5.3 with 2 M and Coded PHY for either speed or range, plus 802.15.4 for Thread/Zigbee/Matter—covering the majority of modern IoT transports with one tiny chip.

ESP32-H2 Overview, Specifications & Applications

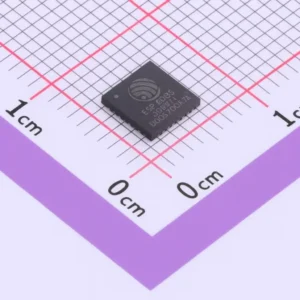

ESPRESSIF’s ESP32-H2 is a highly integrated low-power SoC that pairs a 32-bit single-core RISC-V microprocessor (up to 96 MHz) with dual radios: Bluetooth® Low Energy (Bluetooth 5.3 certified) and IEEE 802.15.4 for Thread, Zigbee 3.0 and Matter. It brings 320 KB SRAM, 128 KB ROM, 4 KB low-power memory, and in-package Quad-SPI flash (2 MB or 4 MB variants) in a compact 4 × 4 mm QFN-32 package—ideal for space-constrained, battery-powered IoT nodes.

On the wireless side, ESP32-H2’s LE PHY supports 1 Mbps, 2 Mbps, and Long-Range Coded PHY (500 kbps/125 kbps), plus LE Advertising Extensions, multiple advertising sets, LE power control, and Bluetooth mesh—making it a versatile platform for both point-to-point and large mesh deployments. Its 802.15.4 subsystem implements the 2.4 GHz O-QPSK PHY at 250 kbps and a feature-rich MAC, providing the foundation for modern smart-home stacks such as Thread, Zigbee, and Matter. In fact, when you combine ESP32-H2 with an ESP Wi-Fi SoC, you can build a Thread Border Router or Matter bridge with minimal external components.

The SoC integrates a broad set of digital and analog peripherals for control and sensing: 19 programmable GPIOs; SPI (with Dual/Quad/QPI), UART, I²C, I²S; Remote Control (RMT); LED PWM (six channels); MCPWM for motor/lighting control; GDMA (3 TX/3 RX); a TWAI® (ISO 11898-1/CAN 2.0) controller; a 12-bit SAR ADC (up to five channels); temperature sensor; and a full-speed USB Serial/JTAG controller that eliminates the need for an external USB-UART bridge and JTAG pod.

Security is first-class: hardware accelerators for AES-128/256, SHA-1/224/256, RSA, ECC/ECDSA; HMAC and Digital Signature peripherals; Secure Boot; XTS-AES external-flash encryption; true RNG; Access Permission Management (APM) and PMP; and a built-in Power Glitch Detector for tamper resilience. These blocks offload crypto from the CPU, harden keys, and help achieve compliance goals without large code footprints.

For energy-sipping designs, the Power Management Unit (PMU) supports Active, Modem-sleep, Light-sleep, and Deep-sleep modes. With LP memory retention, typical Deep-sleep current is just 7 µA, enabling multi-year coin-cell applications. The system timer, two 54-bit GPTimers, three watchdogs (plus a super watchdog), and the Event Task Matrix (ETM) allow rich peripheral-to-peripheral workflows with minimal CPU wakeups—further extending battery life.

The functional block diagram on page 2 illustrates this balanced architecture: the RISC-V CPU and memory subsystem at the core, the Bluetooth LE and 802.15.4 basebands with integrated 2.4 GHz RF (PA/LNA/Balun), the rich digital/analog peripherals, and the security enclave—tied together by the IO-MUX/GPIO matrix and GDMA.

From a physical standpoint, the QFN-32 (4 × 4 mm) package drawing on page 63 shows the tiny footprint and land pattern, supporting dense layouts and cost-effective mass production.

Key specifications

| Parameter | Details |

|---|---|

| CPU & Architecture | 32-bit RISC-V single-core MCU, up to 96 MHz; RV32IMAC with 4-stage pipeline; debug via USB-JTAG/JTAG; instruction trace encoder. |

| CoreMark® | 303.38 at 96 MHz (≈ 3.16 CoreMark/MHz). |

| Memory (on-chip) | 128 KB ROM; 320 KB SRAM (HP); 4 KB LP SRAM retained in Deep-sleep; 4096-bit eFuse (≈ 1792 bits user). |

| In-package Flash | 2 MB (ESP32-H2FH2S) or 4 MB (ESP32-H2FH4S), Quad-SPI, up to 64 MHz; >100 k P/E cycles, >20-year retention. |

| External Memory | SPI/Dual/Quad/QPI flash up to 16 MB mapped via 16 KB cache; XTS-AES encryption/decryption. |

| GPIO | 19 programmable GPIOs (including LP-capable pins), three strapping pins (GPIO8/9/25). |

| Digital Interfaces | SPI2 (master/slave, up to 48 MHz, 1/2/4-line & QPI; six CS); 2×UART (5 MBd, RS-485, IrDA); 2×I²C (100/400 kbit/s); I²S (up to 40 MHz BCK, PDM/TDM/PCM); RMT (2 TX/2 RX); GDMA (3 TX/3 RX); PARLIO; MCPWM; TWAI® (ISO 11898-1/CAN 2.0). |

| Analog Interfaces | 12-bit SAR ADC (up to 5 channels), temperature sensor; two analog pad voltage comparators. |

| USB | USB 2.0 Full-Speed (12 Mbit/s) Serial/JTAG with internal PHY; CDC-ACM serial + integrated JTAG adapter. |

| Timers & WDT | 1×52-bit system timer; 2×timer groups (54-bit counters); 3×digital WDT + super watchdog; ETM for event-task routing. |

| Bluetooth LE | Bluetooth 5.3 certified; 1 M/2 M/Coded PHY (125/500 kbps); advertising extensions/multiple sets; simultaneous roles; LE power control; Bluetooth mesh. |

| 802.15.4 | IEEE 802.15.4-2015 compliant; 2.4 GHz O-QPSK, 250 kbps PHY; MAC with CSMA/CA, auto-ACK, CSL; supports Thread, Zigbee 3.0, Matter and other stacks. |

| RF TX Power | Programmable from –24 dBm to +20 dBm (LE and 802.15.4). |

| RX Sensitivity (typ.) | BT LE Coded 125 kbps: –106.5 dBm; LE 500 kbps: –102.5 dBm; 802.15.4 250 kbps: –102.5 dBm. |

| Security | Secure Boot (RSA/ECDSA); flash encryption (XTS-AES); AES-128/256; SHA-1/224/256; RSA/ECC/ECDSA; HMAC; Digital Signature; RNG; APM/PMP; Power Glitch Detector. |

| Power Modes | Active / Modem-sleep / Light-sleep / Deep-sleep; LP memory retained; Deep-sleep ≈ 7 µA. |

| Supply & Temp | 3.0–3.6 V recommended; –40 °C to +105 °C ambient. |

| Package | QFN-32 (4 × 4 mm); reference land pattern available. |

| Notable Pin Functions | USB D± on GPIO26/27 (default to USB); JTAG on MTDI/MTCK/MTMS/MTDO; UART0 on GPIO23/24; ADC on GPIO1–5. |

Visual aids: see the functional block diagram on page 2 for subsystem interconnects and the package drawing on page 63 for mechanical details and pad layout.

Applications

Matter & Thread end devices

With 802.15.4 + BLE in one die, ESP32-H2 is a natural fit for Matter over Thread end nodes—sensors, switches, plugs, locks, small appliances, and battery-operated controllers. LE can simplify onboarding (e.g., BLE-based commissioning) while Thread provides robust mesh transport. Deep-sleep with LP memory ensures long battery life, and the ETM/GDMA let peripherals move data without frequent CPU wakeups.

Thread Border Routers & Matter Bridges

Combine ESP32-H2 with an ESP Wi-Fi SoC to implement a full Thread Border Router or a bridge between Matter ecosystems and legacy Zigbee/Thread accessories. This pairing leverages ESP32-H2’s 802.15.4 MAC/PHY and security engine together with the companion’s Wi-Fi/Ethernet backhaul. USB-Serial/JTAG makes development and field service straightforward without extra hardware.

Smart lighting & building controls

Six-channel LED PWM (dithering, gamma-curve fading) enables smooth dimming and color control for lamps and luminaires. MCPWM offers synchronized drive for LED power stages or motorized shades. TWAI® (CAN 2.0) support and PARLIO broaden gateway and building-automation use cases where wired fieldbuses or parallel interfaces still matter.

Industrial and commercial sensing

Use the 12-bit SAR ADC and analog comparators for threshold-based wakeups, and the temperature sensor for thermal monitoring. RMT handles IR/remote protocols or precise pulse capture; PCNT counts flow or encoder pulses; two I²C controllers connect to sensor arrays; SPI/I²S and GDMA move data efficiently in bursty duty cycles. With secure boot and encrypted flash, firmware integrity is protected even at the edge.

Wearables and medical wellness devices

The tiny 4 × 4 mm package, integrated RF (PA/LNA/Balun), and 7 µA Deep-sleep enable compact designs that still meet aggressive battery targets. Bluetooth LE Long Range extends coverage; multiple roles/sets facilitate beacons and concurrent connections; privacy features and LE Secure Connections improve user trust.

Consumer electronics accessories

BLE + 802.15.4 lets accessory makers support both classic BLE app control and standards-based smart-home networks. USB Serial/JTAG accelerates development and manufacturing tests, while the watchdog suite and power-glitch detector add resilience under brownout or ESD events.

“Small features” (quick highlights)

-

RISC-V @ 96 MHz + CoreMark-optimized performance in a compact, cost-effective design.

-

USB Serial/JTAG on-chip for plug-and-play flashing, logging, and debugging—no external bridges.

-

19 flexible GPIOs with an IO-MUX/GPIO matrix that can route 70+ peripheral signals for agile pin planning.

Developer notes

-

Pin planning: Some pins are multiplexed with JTAG and USB D± by default; free them via configuration if needed. Observe strapping-pin states on GPIO8/GPIO9/GPIO25 during boot. The pin tables in Chapter 2 summarize IO-MUX and analog functions at reset/after reset.

-

RF targets: TX power is software-configurable up to +20 dBm; LE long-range sensitivity reaches –106.5 dBm, and 802.15.4 hits –102.5 dBm for robust mesh coverage.

-

Power rails: Operate from a single 3.0–3.6 V supply; adhere to the power-up timing diagram (page 21) and don’t leave CHIP_EN floating.

-

Mechanical: Refer to the package drawing on page 63 and download the recommended land pattern to speed PCB layout.

-

Stacks & tools: Develop with ESP-IDF; Thread/Zigbee/Matter and Bluetooth Mesh are supported by Espressif’s SDKs and documentation portals referenced in the datasheet’s resources.

Specifications

Compute & memory. The ESP-RISC-V CPU delivers zero-wait access to on-chip SRAM/cache, vectored interrupts (up to 28 external), PMP/PMA regions, and a standards-compliant debug module. The internal 320 KB SRAM plus 4 KB LP SRAM comfortably host RTOS tasks and networking stacks; in-package 2 MB/4 MB Quad-SPI flash stores firmware; external QSPI/QPI flash up to 16 MB is supported for larger images and OTA partitions—protected by XTS-AES.

Peripherals. Two UARTs and two I²C controllers handle common device interfacing. SPI2 supports up to 48 MHz in master mode with six chip-selects for multiple slaves. I²S covers PCM/TDM/PDM with a BCK up to 40 MHz, suitable for voice hubs or ultrasonic ranging. The LEDC offers 20-bit duty resolution with linear and gamma fading; MCPWM adds capture, fault, and synchronization for motors or high-power LED drivers. RMT, PCNT, and PARLIO address IR control, pulse/encoder counting, and parallel streaming—all backed by the six-channel GDMA.

Connectivity. Bluetooth LE 5.3 adds multiple concurrent roles, power control, and privacy; 802.15.4’s MAC includes hardware frame filtering, auto-ACK, CSL for power-efficient rendezvous, and comprehensive blocking/selectivity. These radios share a calibrated 2.4 GHz front-end (PA/LNA/Balun) and on-chip PLL/clock generator.

Security. Alongside cryptographic accelerators and secure boot, the device integrates a Digital Signature peripheral for key-protected signing, HMAC for challenge–response, and an anti-DPA pseudo-round design in AES/XTS. The Access Permission Management and PMP provide fine-grained isolation across high-performance (HP) and low-power (LP) domains and DMA masters. A power-glitch detector monitors VDD rails to mitigate fault-injection tampering.

Power & reliability. Light-sleep and Deep-sleep modes switch off RF and most clocks but keep LP timers/memory alive for fast resume. Typical Deep-sleep current is ~7 µA; modem-sleep varies with clocking and peripheral gating (see current tables). The chip is qualified for industrial temperatures (-40 °C to +105 °C) and tested for ESD/HTOL/TCT/uHAST, supporting robust deployments.

ESP32-H2FH2S vs ESP32-H2FH4S Comparison

| Aspect | ESP32-H2FH2S | ESP32-H2FH4S |

|---|---|---|

| In-package flash | 2 MB Quad-SPI | 4 MB Quad-SPI |

| CPU / radio | 32-bit RISC-V (up to 96 MHz), Bluetooth LE 5.x, IEEE 802.15.4 (Thread/Zigbee/Matter) | 32-bit RISC-V (up to 96 MHz), Bluetooth LE 5.x, IEEE 802.15.4 (Thread/Zigbee/Matter) |

| On-chip RAM | 320 KB SRAM + 4 KB LP SRAM | 320 KB SRAM + 4 KB LP SRAM |

| ROM / eFuse | 128 KB ROM; eFuse for keys/config | 128 KB ROM; eFuse for keys/config |

| Peripherals | 19 GPIOs; UART, SPI, I²C, I²S, RMT, LEDC, MCPWM, GDMA, USB Serial/JTAG, TWAI®, 12-bit ADC | 19 GPIOs; UART, SPI, I²C, I²S, RMT, LEDC, MCPWM, GDMA, USB Serial/JTAG, TWAI®, 12-bit ADC |

| Package | QFN-32 (4 × 4 mm) | QFN-32 (4 × 4 mm) |

| Typical use cases | Cost-optimized designs, simple BLE/Thread endpoints, beacons, basic sensors/actuators with modest firmware | Feature-rich endpoints, dual-OTA workflows, Matter devices with larger stacks/resources, room for logs/assets |

| Partitioning headroom (typical) | Tight for A-only app or small A/B OTA if app is compact | Comfortable for A/B OTA, larger Matter/Thread + features |

| BOM impact | Lowest cost | Slightly higher cost for more flash |

Practical guidance

When to pick ESP32-H2FH2S (2 MB)

-

Ultra-low-cost nodes: simple sensors, buttons, beacons, basic Zigbee/Thread endpoints.

-

Firmware image is small and stable (e.g., no need for big assets or multiple stacks).

-

You’re okay with single-slot OTA (replace-in-place) or infrequent updates handled offline.

When to pick ESP32-H2FH4S (4 MB)

-

Matter over Thread devices where stacks, clusters, and translation layers grow over time.

-

You want A/B OTA (download new image alongside the current one, then swap) for safer updates.

-

Extra room for diagnostics: persistent logs, crash dumps, calibration/NVS data, or a small filesystem.

Example partition planning (illustrative)

-

2 MB flash:

-

Bootloader + OTA data + NVS + PHY/Cal: ~200–300 KB total

-

App slot: ~1.6–1.7 MB (single-slot OTA recommended)

-

-

4 MB flash:

-

Same overheads as above

-

Two app slots at ~1.6 MB each for A/B OTA (or one large app + assets)

-

Tip: keep some margin (≥10%) for future SDK and stack growth; Matter devices especially benefit from 4 MB.

What stays identical

-

RF performance, CPU speed, low-power modes, electrical/thermal ratings, pinout, and peripheral set are the same between FH2S and FH4S. Your PCB, RF layout, and firmware (besides partition map) are effectively interchangeable.

Selection checklist

-

Do you need A/B OTA or frequent field updates? → ESP32-H2FH4S

-

Is your app <~1.6 MB and unlikely to grow? → ESP32-H2FH2S can be fine

-

Building Matter or feature-rich Thread/Zigbee endpoints? → Prefer ESP32-H2FH4S

-

Tightest BOM target, simplest endpoint? → ESP32-H2FH2S

Specification: ESPRESSIF ESP32-H2 Bluetooth LE & IEEE 802.15.4 MCU

|