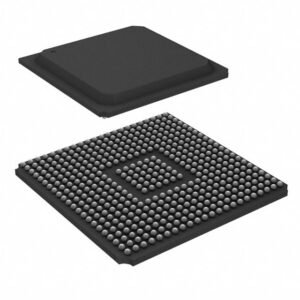

Xilinx/AMD

Xilinx—now part of AMD—created the first commercial FPGA and turned reconfigurable hardware into a mainstream platform for high-performance, low-latency computing. From the early Virtex and Spartan families to modern Kintex/Artix devices and Zynq SoCs, the company enabled engineers to implement custom hardware in weeks rather than the months or years required for ASICs.

In the 2010s Xilinx raised the bar with 2.5D interposer technology, the processor-centric Zynq-7000 and Zynq UltraScale+ families, and the tightly integrated RFSoC line that brings multi-GSPS converters onto the same die as programmable logic. For the cloud and enterprise, Alveo PCIe cards accelerate AI inference, database operations, compression, and video processing at compelling performance-per-watt. At 7 nm, Versal ACAP devices add AI Engines and a scalable network-on-chip for heterogeneous acceleration from edge to data center.

Developers rely on Vivado for RTL design and timing closure, Vitis for software-first acceleration in C/C++/OpenCL with HLS, and rich IP libraries for interfaces like PCIe®, Ethernet, HDMI 2.1, JESD204, and MIPI. Industries spanning 5G/O-RAN, industrial automation, automotive ADAS, aerospace & defense, medical, broadcast, and HPC choose (AMD) Xilinx for deterministic latency, reconfigurability, and long lifecycles.

Following the Feb 2022 acquisition, the portfolio continues under AMD branding (AMD Versal, AMD Zynq UltraScale+, AMD Alveo, AMD Kria). For procurement and search, “Xilinx” remains a critical keyword, reflecting decades of documentation, training, and community knowledge. If you need adaptable compute with exacting power, latency, and reliability targets, the AMD (formerly Xilinx) stack offers a proven path from prototype to production.

Showing all 8 results

Key Features:

✅ XC7VX485T-2FFG1761C FPGA – High-speed GTX transceivers (16Gbps) ✅ 1GB DDR3 + PCIe Gen2x8 – Advanced memory & interface support ✅ FMC HPC Connectors – Expand with mezzanine cards for custom I/OKey Features:

✅ Ultra-Low Power – 13μA quiescent current, DataGATE for dynamic power reduction ✅ High-Speed Logic – 5.7ns pin-to-pin delay, DualEDGE flip-flops for 2x efficiency ✅ Flexible I/O Banking – Supports LVCMOS, LVTTL, SSTL, HSTL (1.5V–3.3V)Key Features:

✅ Multi-Gigabit Transceivers: 4 RocketIO for high-speed serial comms (up to 3.125Gbps) ✅ Integrated PowerPC 405 CPU: RISC-based embedded processing ✅ High-Density Logic: 6,768 cells, 752 CLBs, and 516Kb RAM for complex designsKey Features:

✅ High Logic Density – 1.5M gates, 1,542 logic cells ✅ Rich I/O Options – 316 user I/O, supports LVCMOS, LVTTL, HSTL, SSTL ✅ DSP & RAM Resources – 1,728Kb BRAM, embedded multipliersKey Features

✅ Ultra-Low Power (0.35mW Static) – 90nm process, ideal for battery-powered & rugged applications. ✅ High-Speed I/O & DSP Support – 667MHz operation with embedded multipliers for signal processing. ✅ Multi-Voltage Compatibility (1.2V–3.3V) – Flexible I/O standards (LVCMOS, LVTTL, HSTL, SSTL).Key Features

✅ 3.75Gbps RocketIO GTP Transceivers – High-speed serial links for PCIe, SATA, and 5G backhaul. ✅ 550MHz DSP48E Slices – 25×18 multipliers + 48-bit accumulators for real-time signal processing. ✅ Advanced 65nm Low-Power Design – 1V core voltage with integrated thermal/power monitoring.Key Features

✅ 6.5Gbps RocketIO GTX Transceivers – Supports PCIe Gen2, SATA, 10G Ethernet, and CPRI. ✅ High-Capacity Logic Fabric – 131K logic cells with 6-input LUTs for complex designs. ✅ Power-Optimized 40nm Architecture – 1.0V core voltage with triple-oxide technology for reduced leakage.Key Features

✅ High-Density Logic Fabric: 241K logic cells with 6-input LUTs for complex designs. ✅ Ultra-Fast Serial Connectivity: 6.6Gbps GTX transceivers (PCIe Gen2/3, 10G Ethernet). ✅ Extended Temperature Range: -40°C to +100°C for harsh environments.Status: Acquired by AMD (deal announced Oct 2020; closed Feb 14, 2022). Since mid-2023 most product lines are branded AMD (formerly Xilinx), but engineers and buyers still commonly search for “Xilinx FPGAs,” “Xilinx Zynq,” and “Xilinx Vivado.”

Headquarters (historical): San Jose, California, with major sites in Longmont (US), Dublin (IE), Singapore, Hyderabad (IN), Beijing/Shanghai (CN), Brisbane (AU), Tokyo (JP), and Yerevan (AM).

1) Xilinx Overview

Xilinx, Inc. was the company that invented the first commercially viable field-programmable gate array (FPGA) and popularized the fabless semiconductor business model. For four decades the brand became synonymous with programmable logic, enabling hardware that can be reconfigured after manufacturing to accelerate evolving workloads, reduce risk versus ASICs/ASSPs, and deliver deterministic, low-latency performance.

Today the portfolio—now under AMD—spans FPGAs, adaptive SoCs, RFSoCs, data-center accelerator cards, SOMs (Kria), extensive IP cores, and a modern software toolchain (Vivado, Vitis, HLS). These solutions power applications across 5G/Open RAN, data centers & HPC, industrial/robotics, automotive ADAS, aerospace & defense, medical imaging, broadcast/pro-AV, and test & measurement.

2) History & Milestones

-

1984: Founded by Ross Freeman, Bernard Vonderschmitt, and James V. Barnett II in Silicon Valley. Freeman’s insight: programmable chips that behave like a “blank tape,” letting engineers implement custom hardware post-fabrication.

-

1985–1995: First commercial FPGAs ship; rapid revenue growth; expansion to Europe and Asia; IPO on Nasdaq.

-

Late 1990s–2000s: Growth of the Virtex (high performance) and Spartan (cost-optimized) families; introduction of embedded soft processors (MicroBlaze), rich IP catalogs, and ISE toolchain.

-

2011–2014: Breakthrough 2.5D Stacked Silicon Interconnect (SSI) and the Virtex-7 2000T—a milestone device using a silicon interposer to combine multiple FPGA die; Zynq-7000 launches, fusing ARM Cortex-A9 processors with programmable logic; Vivado Design Suite debuts as the next-gen tool environment; UltraScale (20 nm) and later UltraScale+ (16 nm FinFET) families arrive.

-

2017–2021: Rise of data-center acceleration with Alveo cards; Zynq UltraScale+ RFSoC integrates wideband RF ADC/DACs covering sub-6 GHz with mmWave interfaces for 5G; shipments of the Versal family begin—introducing the ACAP concept (Adaptive Compute Acceleration Platform) at 7 nm with dedicated AI Engines, DSP tiles, programmable logic, and a network-on-chip.

-

2022–2023: AMD acquires Xilinx; brand transition to AMD while the engineering DNA, roadmaps, and families (Versal, Zynq, UltraScale+, Alveo, Kria) continue under AMD’s Adaptive and Embedded Computing Group.

3) Product Families (What Engineers Buy)

FPGAs & Adaptive SoCs

-

Virtex® (incl. UltraScale/UltraScale+): maximum logic density, highest-speed serial transceivers, DSP, and memory bandwidth for line cards, radar/EW, cutting-edge test gear, and scientific instruments.

-

Kintex® (incl. UltraScale/UltraScale+): performance/value balance for 10–100 G networking, vision, and medical/industrial systems.

-

Artix®-7: low power, small form factors with integrated transceivers for portable instrumentation, vision modules, and communications endpoints.

-

Spartan®-7/-6 (legacy): cost-optimized programmable logic for displays, consumer/industrial control, and embedded I/O glue logic.

-

Zynq®-7000 SoC: ARM Cortex-A9 + FPGA fabric ideal for edge analytics, vision, and control; supported by PetaLinux, Yocto layers, and rich IP.

-

Zynq® UltraScale+™ MPSoC: 64-bit multi-core ARM processors, real-time cores, GPU, safety/security features plus programmable logic—suited for ADAS, robotics, factory automation, and deterministic control.

-

Zynq® UltraScale+™ RFSoC: integrates multi-GSPS RF data converters + programmable logic for 5G radios, phased array, cable access, EW—cutting BOM and latency.

-

Versal™ ACAP (AI Core/AI Edge/Prime/Premium/HBM): heterogeneous 7 nm devices with AI Engines, DSPs, PL fabric, and NoC—scalable from embedded edge AI to coherent, HBM-fed data-center acceleration.

Data-Center & Edge Modules

-

Alveo™ accelerator cards (U200/U250/U280/U50/U55C etc.): PCIe cards using UltraScale+ devices (some with HBM2) for inference, database, video transcode, search, compression, and networking offload—often delivering lower TCO via performance-per-watt and latency advantages.

-

Kria™ SOMs: production-ready system-on-modules with pre-built stacks (vision, robotics), reference apps, and starter kits to accelerate from prototype to deployment.

CPLDs & Legacy

-

CoolRunner® / 9500 CPLDs support ultra-low-power control logic and fast I/O bridging where tiny footprints and deterministic timing matter.

4) Tools, Software & IP

-

Vivado® Design Suite: RTL-to-bitstream flow with powerful timing closure, incremental compile, CDC, and debug (ILA/VIO).

-

Vitis™ Unified Software Platform: brings C/C++/OpenCL development, libraries, and accelerated kernels to programmable logic and ACAP; integrates HLS for algorithmic design.

-

Vitis AI & Model Zoo: optimized DNNs, quantization flow, and runtime for Versal/Zynq platforms.

-

IP & Reference Designs: from basic DSP (FIR/FFT) to complex cores (PCIe®, Ethernet, HDMI 2.1, JESD204B/C, MIPI), plus platform reference designs for vision, motor control, radar, and software-defined radio.

-

Ecosystem: tutorials, PetaLinux BSPs, board support packages, MicroBlaze soft processor, community overlays (e.g., PYNQ), and cloud-scale options like AWS F1 for FPGA acceleration.

5) Why (AMD) Xilinx Matters

-

Programmability across lifecycles: Ship hardware today, push new bitstreams or firmware later—ideal for fast-moving standards (5G/O-RAN), security updates, and long-life industrial gear.

-

Latency and determinism: FPGA/ACAP datapaths bring microseconds-level latency and hard real-time behavior that general-purpose GPUs/CPUs struggle to match.

-

Performance-per-watt: Custom pipelines, dataflow architectures, and on-chip memory/hard blocks optimize energy efficiency—vital for edge inference and dense racks.

-

Heterogeneous integration: From RF converters to AI Engines and NoC, modern devices collapse entire boards into a single adaptive SoC, cutting BOM, power, and size.

-

Safety & security: Industrial and functional safety certifications (e.g., IEC 61508 SIL levels on select families) and hardened security features support regulated markets.

6) Markets & Use Cases

-

Communications & 5G: Massive MIMO, beamforming, fronthaul/backhaul, packet processing, telco acceleration (O-RAN DU/RU).

-

Automotive: ADAS sensor fusion, domain/zonal controllers, in-vehicle networking, perception pipelines; powertrain and body electronics with deterministic control.

-

Industrial/Robotics: Vision-guided robots, deterministic motion control, real-time Ethernet, predictive maintenance, machine safety.

-

Aerospace & Defense: EW/ELINT, SDR, radar/sonar, space-grade programmable logic with radiation-tolerant flows.

-

Medical & Life Sciences: Ultrasound, endoscopy, high-speed imaging, genomics acceleration, low-latency video.

-

Data Center & HPC: Inference/training assist, database analytics, video transcoding, compression, smartNIC/DPUs, HBM-enabled memory bandwidth.

-

Broadcast & Pro-AV: HDMI 2.1/8K pipelines, low-latency live production, LED walls, routing/switching.

7) Innovation Highlights

-

Commercial FPGA inventor—set the template for programmable logic as a mainstream alternative to ASICs.

-

First high-volume 2.5D interposer FPGA (Virtex-7 2000T), pioneering chiplet-style integration in production.

-

Zynq architecture: processor-centric SoC + programmable logic changed embedded design flows.

-

RFSoC integration: on-chip multi-GSPS converters shrank radio cards and eliminated entire IF stages.

-

Versal ACAP: 7 nm heterogeneous compute with AI Engines, bringing software-like agility to hardware.

8) Brand Transition: From Xilinx to AMD

In February 2022 AMD completed its all-stock acquisition of Xilinx (≈$60 B). Through 2023, product branding transitioned to AMD (e.g., AMD Versal, AMD Zynq UltraScale+, AMD Alveo, AMD Kria). For procurement and SEO, it remains useful to reference “Xilinx” alongside AMD to capture legacy search behavior and documentation.

9) Practical Buying Tips (for engineers & buyers)

-

Start with I/O & memory needs: transceiver count/speed (e.g., 25G/32G/58G), external memory (DDR4/LPDDR4/DDR5/HBM), on-chip BRAM/URAM.

-

Compute mix: balance DSP slices, AI Engines (Versal), and PL fabric versus power/latency targets.

-

Thermals & form factor: check speed grade, temperature range, and package (FF, FL, CS, etc.); review heatsink/airflow budgets early.

-

Tool flow & IP: confirm Vivado/Vitis versions, licensed IP, and board support up front; pilot the design with an evaluation kit or Kria SOM to de-risk schedules.

-

Longevity: verify lifecycle/PCN/obsolescence plans, especially for industrial and automotive programs.