MPF500TL-FCG1152I Microchip MPF500TL-FCG1152I Field Programmable Gate Arrays (FPGAs)

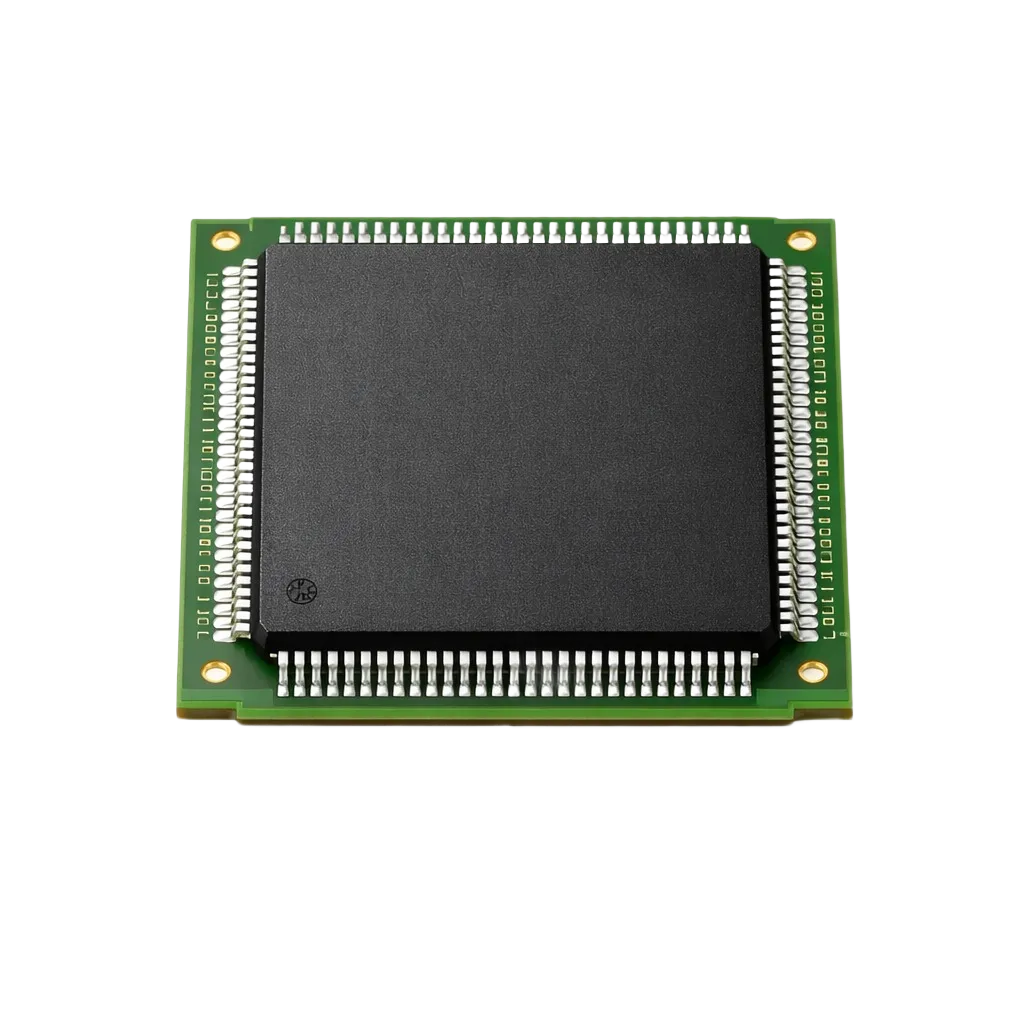

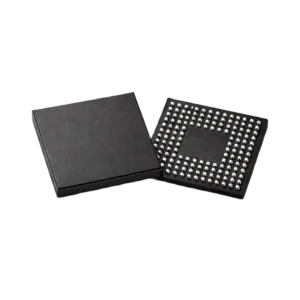

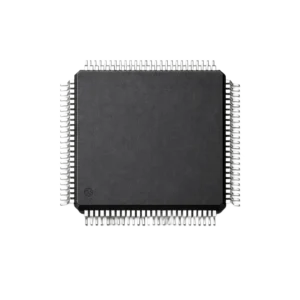

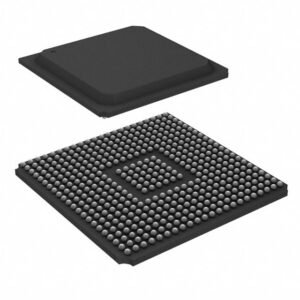

Microchip MPF500TL-FCG1152I FPGA MPF500T 481000 Logic Elements 28nm Technology 1V 1152-Ball BGA Tray

Microchip MPF500TL-FCG1152I Field Programmable Gate Arrays (FPGAs) Overview

The Microchip FPGA MPF500T is a state-of-the-art Field Programmable Gate Array (FPGA) designed to deliver exceptional performance and flexibility for a wide range of applications. Utilizing advanced 28nm technology, this FPGA features 481,000 logic elements and operates at a voltage of 1V, making it an ideal choice for high-density designs. Packaged in a 1152-ball FCBGA format, it ensures efficient thermal management and reliable connectivity, catering to the needs of modern electronic systems.

Key Features of Microchip MPF500TL-FCG1152I Field Programmable Gate Arrays (FPGAs)

- Optimized to 481,000 Logic Elements, improving robustness in practical applications.

- Built to 1V Operating Voltage, making integration easier across a wide range of systems.

- Optimized to advanced 28nm Technology, improving robustness in practical applications.

- Engineered to lifecycle Status: Production, supporting dependable performance in real-world designs.

- Engineered to roHS: Non-Compliant, supporting dependable performance in real-world designs.

- Engineered to 1152-Ball FCBGA Package, supporting dependable performance in real-world designs.

Microchip MPF500TL-FCG1152I Field Programmable Gate Arrays (FPGAs) Applications

Ethernet / Switching / Routing

- Commonly applied in 10G/25G Ethernet PCS/MAC bridging module — 10G/25G Ethernet, SERDES, XGMII, PHY, supporting stable and efficient system performance.

- Often used in vXLAN/Geneve encapsulation/decapsulation offload — tunneling, UDP, checksum, 25G/100G, where predictable behavior and reliability are important.

- Well-suited for line-rate packet mirroring and lawful intercept tap — SPAN, mirror, timestamp, 10G/25G, helping designers meet typical integration requirements.

- Often used in cut-through packet forwarding for low-latency networks — L2/L3, low-latency pipeline, SERDES, where predictable behavior and reliability are important.

- Well-suited for tSN traffic shaping endpoint — TSN, 802.1Qbv, 802.1AS, PTP, helping designers meet typical integration requirements.

Display / HDMI / DP / LED Wall

- Commonly applied in display systems use FPGAs for bridging, timing generation, overlay, calibration, and controlling large LED matrices. They excel in deterministic pixel pipelines, high-speed video I/O glue, and multi-panel synchronization where microsecond-to-nanosecond alignment matters, supporting stable and efficient system performance.

- Often used in lED wall scan controller with gamma correction — LED scan, PWM, gamma LUT, where predictable behavior and reliability are important.

- Often used in lVDS/eDP bridge for embedded panels — LVDS, eDP, timing, where predictable behavior and reliability are important.

- Commonly applied in cable diagnostics and link-quality telemetry for video links — AUX/DDC, stats, logs, supporting stable and efficient system performance.

- Commonly applied in color calibration: 3D LUT load/verify and apply — 3D LUT, calibration, DDR, supporting stable and efficient system performance.

Industrial Ethernet & Fieldbus

- Commonly applied in redundant ring protocol monitor (fast failover assist) — ring, failover, timing, supporting stable and efficient system performance.

- Often used in fieldbus protocol bridge (legacy ↔ Ethernet) — gateways, buffering, timing, where predictable behavior and reliability are important.

- Often used in safety network dual-channel heartbeat monitor logic — safety, heartbeat, redundancy, where predictable behavior and reliability are important.

- Well-suited for pROFIBUS timing assist (legacy integration) — PROFIBUS, UART timing, helping designers meet typical integration requirements.

- Often used in industrial firewall: protocol whitelist + rate limiter — ACL, rate limit, DPI-lite, where predictable behavior and reliability are important.

Data Center Offload / SmartNIC / DPU

- Often used in tLS termination datapath acceleration — TLS, AES-GCM, RSA/ECC, PCIe, where predictable behavior and reliability are important.

- Commonly applied in data stream regex prefilter for log analytics — regex, streaming, DDR, DMA, supporting stable and efficient system performance.

- Commonly applied in load balancer tuple hashing and flow dispatch — ECMP/hash, steering, 25G/100G, supporting stable and efficient system performance.

- Commonly applied in qUIC packet parsing and header protection assist — QUIC, UDP, crypto assist, 100G, supporting stable and efficient system performance.

- Commonly applied in cRC/checksum offload for storage and networking — CRC32/64, inline, 25G/100G, supporting stable and efficient system performance.

AI / ML Acceleration & Pre/Post

- Commonly applied in sparse embedding lookup assist for recommender inference — sparse ops, DDR bandwidth, caching, supporting stable and efficient system performance.

- Often used in sensor fusion pre-processing for autonomous systems — timestamping, PTP, multi-sensor, where predictable behavior and reliability are important.

- Often used in low-latency AI pre/post-processing (NMS, resize, normalize) — image resize, NMS, pipeline, where predictable behavior and reliability are important.

- Well-suited for on-device anomaly detection time-series accelerator — windowing, filters, thresholds, helping designers meet typical integration requirements.

- Well-suited for video analytics: motion detection + ROI extraction — frame differencing, ROI, DDR, helping designers meet typical integration requirements.

Microchip MPF500TL-FCG1152I Specifications

General

| Case/Package | FCBGA |

| Lifecycle Status | Production |

| Number of Pins | 1152 |

| RoHS | Non-Compliant |

Specification: Microchip MPF500TL-FCG1152I Field Programmable Gate Arrays (FPGAs)

|

User Reviews

Only logged in customers who have purchased this product may leave a review.

There are no reviews yet.